# A NEW SYMMETRIC CASCADED MULTILEVEL INVERTER TOPOLOGY WITH REDUCED NUMBER OF POWER ELECTRONIC COMPONENTS Shahab Yousefizad\* Vahab Yousefizad\*\*

Ehsan Fallahi\*\*\*

**Abstract:** Researchers try to improve the multilevel inverters performance or make them more economically proposing new switching algorithms or novel structures. In this paper, a new structure is proposed for symmetric cascaded multilevel inverter which has a simpler structure and uses fewer power switches compared to conventional cascaded inverter. The reduction in the number of power electronic devices will result in the reduction of the economic cost, installation area and switching losses. The proposed structure consists of a number of separate voltage sources at the input side to generate different voltage levels and an H-bridge at the output side. Switches also connect the input voltage sources to the output in a direct form or in series. Input sources can be isolated batteries or renewable energy sources such as solar cells and or fuel cells. Using fundamental switching frequency, the proposed inverter capable of generating 7 levels of voltage at the output, is simulated by use of MATLAB/SIMULINK software. The simulation results confirm the performance accuracy and capability of the proposed inverter to generate different voltage levels.

*Keywords:* Multilevel inverter, Cascaded inverter, Symmetric structure, Asymmetric structure, H-bridge.

\*Student, Department of Electrical Engineering, Tafresh University, Tafresh, Iran.

\*\*Student,Department of Electrical Engineering, Sahand University of Technology, Tabriz, Iran.

\*\*\*Student, Department of Electrical Engineering, Islamic Azad University, Ilam Branch, Ilam, Iran.

## I. INTRODUCTION

Voltage source inverters are categorized into two categories of two-level and multilevel inverters[1]. Multilevel inverters have many advantages over two-level inverters including: higher quality delivery power with lower harmonic at the output [2], use of components with lower voltage ratings, lower switching losses [3], higher efficiency, lower  $\frac{dv}{dt}$  rate at the output and therefore lower stress on the load, higher voltage capacity and better electromagnetic compatibility [4]. Therefore, multilevel inverters have found many uses in industry including: use in micro-grids and distributed generation systems, renewable energy sources interface [5], static compensators [6], motor drivers [7], filters and FACTS devices [8]. Multilevel inverters are categorized into the three main categories of diode-clamped, flying capacitor and cascade[9-12]. Cascaded inverter, uses the lowest number of devices in its structure compared to the other two types [13]. Also, this inverter has higher voltage levels, power (13.8kV & 30MVA) and reliability [14]. Given the ever increasing importance of multilevel inverters over recent years, different schemes have been developed to control these inverters, and the following ones are of special importance amongst these algorithms: sinusoidal pulse width modulation, pulse width modulation with selective harmonic elimination and space vector modulation [15].

## II. CONVENTIONAL CASCADED INVERTER

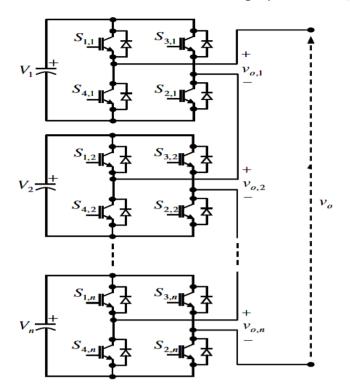

This inverter is comprised of series connection of H-bridges. Each bridge consists of an input voltage source and 4 unidirectional switches with antiparallel diode and can generate three voltage levels of  $+V_{DC}$ , 0 and  $-V_{DC}$  at the output. The cascaded inverter is categorized into two categories of symmetric and asymmetric. The symmetric cascaded inverter uses input voltage source with equal values, and in this status, if n number of input voltage sources exist in each phase, then 2n+1 levels can be obtained in the output voltage [17]. In asymmetric cascaded inverter, input voltage sources have different values and can generate more voltage levels compared to symmetric cascaded inverter at the output. In this case, usually three incremental schemes called unary, binary and trinary are used to select input voltage sources values.

Figure 1. shows conventional cascaded inverter in the single phase form [16].

If n number of input voltage sources exist in the inverter structure, then Equation 1. shows the input sources values in the unary incremental scheme.

$$V_k = kV_1 \quad k = 2, 3, ..., n$$

(1)

Equation 2. shows the input sources values in the binary incremental scheme.

$$V_{k+1} = 2^k V_1$$

k = 1, 2, 3,..., n-1 (2)

Equation 3. shows the input sources values in the trinary incremental scheme.

$$V_{k+1} = 3^k V_1$$

$k = 1, 2, 3, ..., n-1$  (3)

Table 1. shows the number of generatable voltage levels at the output and also the number of switches for single phase conventional cascaded inverter in both symmetric and asymmetric modes.

| Table 1. Conventional cascaded multilevel inverter number of switches and output |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

|                     |                | Asymmetric Mode |                            |                |  |

|---------------------|----------------|-----------------|----------------------------|----------------|--|

|                     | Symmetric Mode | Unary           | Binary                     | Trinary        |  |

| N <sub>level</sub>  | 2n+1           | n(n+1)+1        | 2 <sup><i>n</i>+1</sup> -1 | 3 <sup>n</sup> |  |

| N <sub>switch</sub> | 4n             | 4n              | 4n                         | 4n             |  |

voltages

## III. THE PROPOSED TOPOLOGY

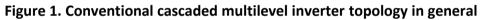

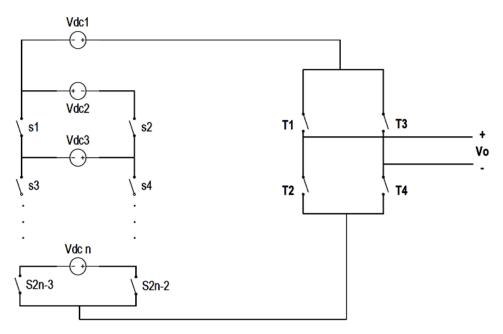

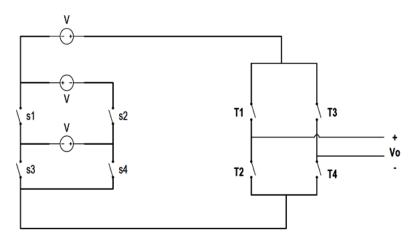

Figure 2. shows the proposed structure for symmetric cascaded inverter. As it is clear from the figure, this inverter consist of n voltage sources at the input side and 2n+2 number of switches. All circuit switches include a unidirectional IGBT with antiparallel diode. The polarity of input sources change alternatively and the H-bridge generates positive and negative voltage levels. Figure 3. shows a schematic comparison between the proposed inverter and conventional cascaded inverter in terms of the number of required power switches.

Figure 2. Proposed topology in general

Figure 3. Comparison of the required number of switches to realize N<sub>level</sub> voltage in conventional and proposed structures

Table 2. shows required switches and input voltage sources for some output voltage levels for proposed topology and conventional topology. According to Figure 3. and Table 2. the proposed inverter uses fewer switches compared to conventional cascaded inverter for the generation of different output voltages, which results in the reduction of the final cost of the inverter, installation area and switching losses.

| Number<br>Sources | of | Input | Number<br>Voltage Lo | - | Switches for Proposed<br>Topology | Switches<br>Conventional<br>Topology | for |

|-------------------|----|-------|----------------------|---|-----------------------------------|--------------------------------------|-----|

| 3                 |    |       | 7                    |   | 8                                 | 12                                   |     |

| 5                 |    |       | 11                   |   | 12                                | 20                                   |     |

| 7                 |    |       | 15                   |   | 16                                | 28                                   |     |

Table 2. Required voltage sources and switches for proposed and conventional topology

#### IV. CASE STUDY

Figure 4. shows the proposed inverter capable of generating 7 levels of output voltage. This inverter consists of 3 input voltage sources and 8 power switches. Table 3. shows the switching states and output voltage for this inverter. In this table, 1 means that the switch is ON and 0 means that the switch is OFF.

| <b>S1</b> | <b>S2</b> | <b>S3</b> | <b>S4</b> | T1 | Т2 | Т3 | Т4 | Vo  |

|-----------|-----------|-----------|-----------|----|----|----|----|-----|

| 0         | 0         | 0         | 0         | 1  | 0  | 1  | 0  | 0   |

| 1         | 0         | 1         | 0         | 1  | 0  | 0  | 1  | V   |

| 0         | 1         | 0         | 1         | 1  | 0  | 0  | 1  | 2V  |

| 0         | 1         | 1         | 0         | 1  | 0  | 0  | 1  | 3V  |

| 1         | 0         | 1         | 0         | 0  | 1  | 1  | 0  | -V  |

| 0         | 1         | 0         | 1         | 0  | 1  | 1  | 0  | -2V |

| 0         | 1         | 1         | 0         | 0  | 1  | 1  | 0  | -3V |

## V. SIMULATION RESULTS

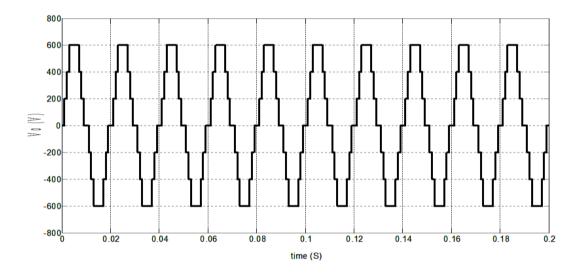

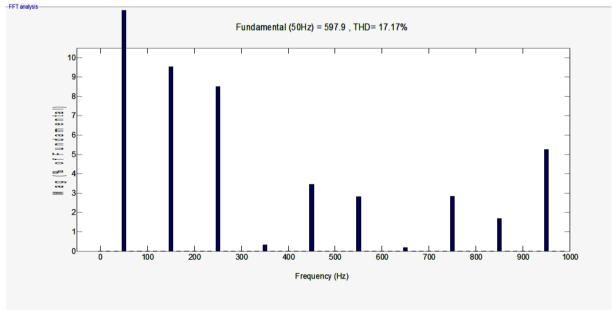

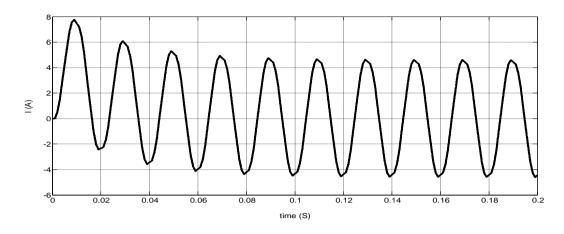

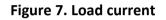

In this section, we focus on the simulation of the inverter shown in the previous section with MATLAB/SIMULINK software. The voltage sources are considered with 200V and inductive ohmic load of L=400mH and R=15 $\Omega$ . Figure 5. shows 7 levels output voltage and Figure 6. shows the harmonic spectrum of the output voltage. Figure 7. shows the load current and Figure 8. shows the harmonic spectrum and load current THD. As it is clear from Figure 7. the load current is approximately sinusoidal which represents the performance accuracy of the proposed inverter.

Figure 5. Output voltage with 7 levels

Figure 8. Harmonic spectrum of load current

## VI. CONCLUSION

In this paper, a new structure has been proposed for symmetric cascaded multilevel inverter that has a simpler circuit and fewer power electronic components compared to the conventional cascaded inverter. The proposed inverter has been simulated by use of fundamental switching frequency and the results of the simulation confirm the performance accuracy of this inverter.

### VII. REFERENCES

[1]Abdul Moeed Amjad and Zainal Salam, "A review of soft computing methods for harmonics elimination PWM for inverters in renewable energy conversion systems,"

Elsevier Journal of Renewable and Sustainable Energy Reviews, 2014, Vol 33, pp. 141–153.

- [2]E. Babaei, S.H. Hosseini, G.B. Gharehpetian, M. Tarafdar Haque and M. Sabahi, "Reduction of dc voltage sources and switches in asymmetricalmultilevel converters using a novel topology," Elsevier Journal of Electric Power Systems Research, 2007, Vol 77, pp. 1073–1085.

- [3]P. Palanivel and S.S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse widthmodulation techniques," IET Power Electron., 2011, Vol. 4, Iss. 8, pp. 951–958.

- [4]Ebrahim Babaei, Mohammad Farhadi Kangarluand Farshid Najaty Mazgar, "Symmetric and asymmetric multilevel inverter topologies with reducedswitching devices,"Elsevier Journal of Electric Power Systems Research, 2012, Vol 86, pp. 122– 130.

- [5]Ali Ajami, Mohammad Reza Jannati Oskuee, Ataollah Mokhberdoran and Alex Van den Bossche, "Developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches," IET Power Electron., 2014, Vol. 7, Iss. 2, pp. 459–466.

- [6]Mohamad Reza Banaei, Mohammad Reza Jannati Oskuee and Hossein Khounjahan, "Reconfiguration of semi-cascaded multilevel inverter to improve systems performance parameters," IET Power Electron., 2014, Vol. 7, Iss. 5, pp. 1106–1112.

- [7]Gierri Waltrich and Ivo Barbi, "Three-Phase Cascaded Multilevel Inverter UsingPower Cells With Two Inverter Legs in Series," IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, AUGUST 2010, VOL. 57, NO. 8, pp. 2605-2612.

- [8]Ilhami Colak, Ersan Kabalci and Ramazan Bayindir, "Review of multilevel voltage source inverter topologies and control schemes," Elsevier Journal of Energy Conversion and Management, 2011, Vol 52, pp. 1114-1128.

- [9]Javad Ebrahimi, Ebrahim Babaei and Gevorg B. Gharehpetian, "A New Multilevel Converter Topology With ReducedNumber of Power Electronic Components," IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, FEBRUARY 2012, VOL. 59, NO. 2, pp. 655-667.

- [10]Charles I. Odeh, Vincent N. Agu and Nentawe Goshwe, "Cascaded three-phase pulse-width modulated switched voltage source inverter," IET Power Electron., 2014, Vol. 7, Iss. 7, pp. 1925–1933.

- [11]Mohammad Farhadi Kangarlu and Ebrahim Babaei, "A Generalized Cascaded Multilevel Inverter UsingSeries Connection of Submultilevel Inverters," IEEE TRANSACTIONS ON POWER ELECTRONICS, FEBRUARY 2013, VOL. 28, NO. 2, pp. 625-636.

- [12]Youhei Hinago and Hirotaka Koizumi, "A Single-Phase Multilevel Inverter Using Switched Series/Parallel DC Voltage Sources," IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, AUGUST 2010, VOL. 57, NO. 8, pp. 2643-2650.

- [13]Kai-Ming Tsang and Wai-Lok Chan, "Single DC source three-phase multilevel inverter using reduced number of switches," IET Power Electron., 2014, Vol. 7, Iss. 4, pp. 775– 783.

- [14]Mariusz Malinowski, K. Gopakumar, Jose Rodriguez and Marcelo A. Pérez, "A Survey on Cascaded Multilevel Inverters," IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, JULY 2010, VOL. 57, NO. 7, pp. 2197-2206.

- [15]José Rodríguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel Inverters: A Survey of Topologies, Controls, and Applications," IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, AUGUST 2002, VOL. 49, NO. 4, pp. 724-738.

- [16]Ebrahim Babaei and Seyed Hossein Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," Elsevier Journal of Energy Conversion and Management, 2009, Vol 50, pp. 2761–2767.

- [17]Hamza Belkamel, Saad Mekhilef, Ammar Masaoud and Mohsen Abdel Naeim, "Novel three-phase asymmetrical cascaded multilevel voltage source inverter," IET Power Electron., 2013, Vol. 6, Iss. 8, pp. 1696–1706.