# THE DRAM PERFORMANCE IN COMPUTER SYSTEM: CHALLENGES AND DEVELOPMENTS OF SYSTEM

P. Lachi Reddy\*

- **Dr. Phool Singh Chouhan\***

- Dr. Senthil Kumar A\*

**Abstract:** The memory structure is a fundamental execution and imperativeness bottleneck in all enrolling systems. Late structure diagram, application, and development floats that require farthest point, information transmission, adequacy, and consistency out of the memory system make it an a great deal more imperative structure bottleneck. Meanwhile, DRAM development is experiencing troublesome advancement scaling challenges that make the upkeep and redesign of its capacity, imperativeness efficiency, and faithful quality by and large more excessive with conventional procedures. In this article, in the wake of depicting the solicitations and troubles stood up to by the memory system, we take a gander at some promising investigation and plan course to thrashing challenges posed by memory scaling. **Keywords:** Memory systems, scaling, DRAM, flash, non-volatile memory, QoS, reliability, hybrid memory, storage

\*Department of Electronics and Communication Engineering, OPJS University, Churu (Rajasthan)

Vol. 5 | No. 1 | January 2016

## **INTRODUCTION**

Modern DRAM devices data rates and column process durations are scaling at various rates with each progressive era of DRAM gadgets. Therefore, the execution attributes of current DRAM memory frameworks are turning out to be harder to assess while they are progressively constraining the execution of present day PC frameworks. Utility and adaptability of the Request Access Distance expository structure, frameworks with contrasting associations and timing parameters are utilized to concentrate the effect of various line process durations, gadget information rates, information burst lengths, t<sub>FAW</sub> control limitations, t<sub>DQS</sub> rank-to-rank information transport exchanging time, the quantity of banks and the quantity of positions in the memory system[1].

The performance attributes of DRAM memory frameworks rely on upon workload particular qualities of get to rates and get to designs. In the Request Access Distance scientific structure, input follows are driven at immersion rates so that the impacts of processor execution can be calculated out from memory framework execution. In spite of the way that the workload follows are driven at immersion rate of the separate memory frameworks, the workload-particular demand get to designs stay important in the analysis of DRAM memory system performance [2].

### **MEMORY SYSTEM TRENDS**

Specifically, on the system/building front, centrality and power utilization have wound up being key graph limiters as the memory structure keeps being responsible for a huge division of general framework hugeness/control. Powerfully and legitimately heterogeneous prepare centers and powers/customers are sharing the memory structure [3]. It is prompting for creating fervor for memory motivation behind detainment and information exchange restrict close to a for the most part new vitality for apparent execution and Quality of Service (QoS) from the memory system. On the applications front, critical applications are ordinarily to incredible degree information centered and are winding up being constantly [4], requiring both consistent and disengaged control of mind blowing measures of information. For instance, bleeding edge genome sequencing movements pass on colossal measures of movement information that overpowers memory stockpiling and trade speed basics of today's amazing desktop and helpful workstation structures yet specialists have the objective of connecting with effortlessness changed medication, which requires in a general sense more information and its persuading examinations. Making of

new executioner applications and use models for PCs likely relies on upon how well the memory structure can bolster the convincing stockpiling and control of information in such information concentrated applications.

#### DRAM Refresh Modes

Computer System performance is continuously compelled by the performance of DRAM based memory systems due to the way that the rate of DRAM memory system performance increase has slacked the rate of processor execution augment in the past thirty years. One reason that DRAM memory system performance has dependably slacked processor performance is that DRAM memory frameworks consistently include no less than one chip that are created and made freely from the processor, and the execution of the interconnected multi-chip DRAM memory framework is inconvenience to scale to achieve higher information rate and lower get to dormancy [5].

#### Memory System Requirements

System fashioners and customers have always required more from the memory structure: world class (ideally, zero inertia and endless exchange speed), unending point of confinement, all at zero cost! The already said designs don't simply fuel and change the above necessities, also incorporate some new essentials. We amass the necessities from the memory system into two orders: exacerbated customary essentials and (for the most part) new necessities [6].

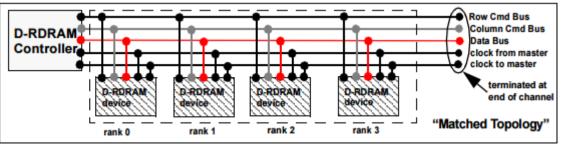

Modern DRAM system with ordinary multi-rank topology can likewise coordinate the crude flagging rates of a Direct RDRAM memory framework. Nonetheless, the downside for these DRAM frameworks is that sit cycles must be planned into the get to convention and committed to framework level synchronization. Thus, notwithstanding when pushed to practically identical information rates, multi-rank DRAM memory frameworks with established framework topologies are less productive as far as information transported per cycle per pin [7].

# **NEW DRAM ARCHITECTURES**

Measure has been the decision innovation for actualizing primary memory because of its moderately low dormancy and minimal effort. Measure prepare innovation scaling has for since quite a while ago empowered lower cost per unit region by empowering diminishments in DRAM cell estimate. Shockingly, additionally scaling of DRAM cells has turned out to be expensive because of expanded assembling intricacy/cost, decreased cell dependability, and possibly expanded cell spillage prompting to high revive rates [8]. As of late, a paper by Samsung and Intel likewise examined the key scaling difficulties of DRAM at the circuit level. They have recognized three noteworthy difficulties as obstructions to viable scaling of DRAM to littler innovation hubs: 1) the developing expense of revives increment in compose idleness and 3) variety in the maintenance time of a cell after some time. In light of such difficulties [9], we accept there are in any event the accompanying key issues to handle with a specific end goal to outline new DRAM models that are a great deal more versatile:

- reducing the negative effect of invigorate on vitality, execution, QoS, and thickness scaling

- 2. improving unwavering quality of DRAM with ease

- 3. improving DRAM parallelism/data transfer capacityinertness and vitality effectiveness

- 4. minimizing information development amongst DRAM and handling components, which causes high inactivity, vitality, and transfer speed utilization, by accomplishing more operations on the DRAM and the memory controllers

- 5. reducing the huge measure of waste present in

#### **Reducing Refresh Impact**

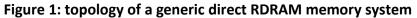

With higher DRAM limit, more cells should be revived at likely higher rates than today. Our late work demonstrates that revive rate limits DRAM thickness scaling: a theoretical 64 GB DRAM gadget would invest 46% of its time and 47% of all DRAM vitality for invigorating its lines, rather than normal 4 GB gadgets of today that invest 8% of the time and 15% of the DRAM vitality on revive. For example, a current supercomputer may have 1PB of memory altogether. In the event that we accept this memory is worked from 8 GB DRAM gadgets and an ostensible revive rate, 7.8kW of force would be exhausted, by and large, just to

invigorate the whole 1PB memory[10]. This is a significant substantial number, just to guarantee the memory effectively keeps its substance! Furthermore, this power is constantly spent paying little mind to how much the supercomputer is used.

Today's DRAM gadgets revive all lines even from a pessimistic standpoint case rate (e.g., each 64ms). In any case, just a little number of feeble columns require a high revive rate (e.g., only~1000 pushes in 32GB DRAM require to be invigorated more much of the time than each 256ms).

### Improving DRAM Reliability

As DRAM innovation scales to littler hub sizes, its unwavering quality turns out to be harder to keep up at the circuit and gadget levels. Indeed, we as of now have confirmation of the trouble of keeping up DRAM unwavering quality from the DRAM chips working in the field today. Our late research demonstrated that a dominant part of the DRAM chips fabricated between 2010-2014 by three noteworthy DRAM merchants show a specific disappointment instrument called push pound: by initiating a line enough circumstances inside an invigorate interim, one can degenerate information in adjacent DRAM columns [11].

This is a case of an unsettling influence mistake where the entrance of a cell causes aggravation of the esteem put away in a close-by cell because of cell-to-cell coupling impacts, some of which are portrayed by our late works. Such obstruction initiated disappointment components are notable in any memory that pushes the cutoff points of innovation, e.g., NAND streak memory. In any case, in the event of DRAM, producers have been very fruitful in containing such impacts up to this point. Unmistakably, the way that

such disappointment instruments have turned out to be hard to contain and that they have as of now slipped into the field demonstrates that failure management in DRAM has turned into a critical issue. We trust this issue will turn out to be significantly more exacerbated as DRAM innovation downsizes to littler hub sizes. Consequently, it is critical to look into both the (new) disappointment components in future DRAM outlines and in addition systems to endure them [12].

### Improving DRAM Parallelism

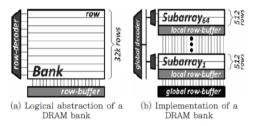

A key limiter of DRAM parallelism is bank clashes. Today, a bank is the finest-granularity autonomously available memory unit in DRAM. In the event that two gets to go to a similar bank, one needs to totally sit tight for the other to complete before it can be begun. We have as of late created systems, called SALP (sub-array level parallelism), that adventure the interior sub-array structure of the DRAM bank to for the most part parallelize two demands that get to a similar bank. The key thought is to lessen the equipment sharing between DRAM sub-arrays with the end goal that gets to a similar bank however unique sub-arrays can be started in a pipelined way.

This component requires the introduction of the inside sub-array structure of a DRAM bank to the controller and the plan of the controller to exploit this structure. Our outcomes demonstrate critical upgrades in execution and vitality productivity of principle memory because of parallelization of solicitations and change of line cradle hit rates [13].

Fig. 3 DRAM Bank Organization and Sub-arrays in a Bank

### Reducing DRAM Latency and Energy

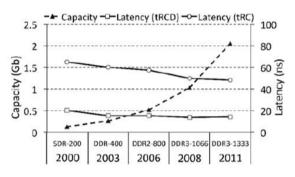

The DRAM business has so far been fundamentally determined by the cost-per-bit metric: give most extreme ability to a given cost. As appeared in Figure 3, DRAM chip limit has expanded by around 16 xs in 12 years whiles the DRAM dormancy diminished by just roughly 20%. This is the consequence of a ponder decision to amplify limit of a DRAM chip while minimizing its cost. We trust this decision should be returned to within the sight of no less than two key patterns. In the first place, DRAM inertness is turning out to be more

imperative particularly for reaction time basic workloads that require QoS ensures. Second, DRAM limit is turning out to be difficult to scale and thus makers' likely need to give new values to the DRAM chips, prompting to more motivators for the creation of DRAMs that are streamlined for goals other than predominantly limit amplification. To alleviate the high region overhead of DRAM detecting structures, item DRAMs associate numerous DRAM cells to every detect speaker through a wire called a bit. These bits have a high parasitic capacitance because of their long length, and this bit line capacitance is the prevailing wellspring of DRAM idleness [14].

Fig. 4 DRAM Capacity & Latency over Time

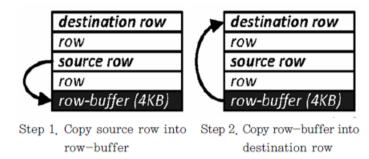

# Exporting Bulk Data Operations to DRAM

Empowering In-Memory Computation Today's frameworks squander noteworthy measure of vitality [15], DRAM transmission capacity and time (and also significant on-chip reserve space) by infrequently superfluously moving information from fundamental memory to processor stores. One case of such wastage once in a whilehappens for mass information duplicate and introduction operations in which a page is replicated to another or instated to esteem. On the off chance that the replicated or introduced information is not instantly required by the processor, performing such operations inside DRAM (with moderately little changes to DRAM) can spare critical measures of vitality, data transfer capacity, and time. We watch that a DRAM chip inside works on mass information at a column granularity. Misusing this interior structure of DRAM can empower page duplicate and instatement to be performed altogether inside DRAM without bringing any information off the DRAM chip. In the event that the source and goal page live inside a similar DRAM sub array, our outcomes demonstrate that a page duplicate can be quickened by more than a request of greatness (~11 times), prompting to a vitality decrease of ~74 times and no wastage of DRAM information transport transmission capacity [16].

Fig. 5 High-level idea behind RowClone's in-DRAM page copy mechanism

#### Minimizing Capacity and Bandwidth Waste

This pressure calculation has low decompression inactivity as the reserve square can be remade utilizing a vector expansion or possibly even vector connection. It diminishes memory transmission capacity necessities, better uses memory/reserve space, while insignificantly affecting the idleness to get to information. Granularity administration and information pressure support can conceivably be incorporated into DRAM controllers or in part gave inside DRAM [17], and such instruments can be presented to programming, which can empower higher vitality reserve funds and higher execution changes. Administration strategies for compacted stores and recollections and adaptable granularity memory framework outlines, programming procedures/plans to take better favorable position of reserve/memory pressure and adaptable granularity, and methods to perform calculations on packed memory information are very encouraging bearings for future research.

### Making NVM Reliable and Secure

As opposed to customary diligent stockpiling gadgets, which work on substantial squares of information (hundreds or a large number of bits) [18], new non-unstable memory gadgets give the chance to work on information at a much littler granularity (a few or several bits). Such operation can extraordinarily streamline the execution of more elevated amount atomicity and consistency ensures by permitting programming to get select access to and perform all the more fine-grained reports on constant information.

Past works have demonstrated that this conduct of NVM gadgets can be abused to enhance framework unwavering quality with new document framework outlines, enhance framework execution and dependability with better check pointing approaches, and plan more vitality effective and higher execution framework design deliberations for capacity and memory. On the other side, the same non-instability can prompt to conceivably unexpected

security and protection issues that don't exist for existing DRAM fundamental recollections: basic and private information [19] (e.g., decoded passwords put away in framework memory) can hold on long after the framework is shut down, and an aggressor can exploit this reality. To battle this issue, some late works have analyzed effective encryption/decoding plans for PCM gadgets.

## CONCLUSION

We have portrayed a few research headings and thoughts to upgrade memory scaling by means of framework and engineering level methodologies. We accept there are three key central rules that are fundamental for memory scaling:

- better participation between gadgets, framework, and programming, i.e., the effective presentation of wealthier data here and there the layers of the framework stack with the advancement of more adaptable yet conceptual interfaces that can scale well into the future,

- Superior to anything most pessimistic scenario plan, i.e., outline of the memory framework to such an extent that it is upgraded for the normal case rather than the most pessimistic scenario,

- 3) Heterogeneity in outline, i.e., the utilization of heterogeneity at all levels in memory framework configuration to empower the improvement of numerous measurements in the meantime. We trust these three standards are connected and at times coupled.

### REFERENCES

- 1. "SAFARI tools," https://www.ece.cmu.edu/safari/tools.html.

- 2. "International technology roadmap for semiconductors (ITRS)," 2011.

- 3. Hybrid Memory Consortium, 2012, http://www.hybridmemorycube.org.

- 4. J.-H. Ahn et al., "Adaptive self refresh scheme for battery operated high-density mobile DRAM applications," in ASSCC, 2006.

- 5. A. R. Alameldeen and D. A. Wood, "Adaptive cache compression for highperformance processors," in ISCA, 2004.

- 6. C. Alkan et al., "Personalized copy-number and segmental duplication maps using next-generation sequencing," in Nature Genetics, 2009.

- 7. G. Atwood, "Current and emerging memory technology landscape," in Flash Memory

Summit, 2011.

- 8. R. Ausavarungnirun et al., Staged memory scheduling: Achieving high performance and scalability in heterogeneous systems," in ISCA, 2012.

- 9. R. Ausavarungnirun et al., "Design and evaluation of hierarchical rings with deflection routing," in SBAC-PAD, 2014.

- S. Balakrishnan and G. S. Sohi, "Exploiting value locality in physical register files," in MICRO, 2003.

- 11. Bhattacharjee and M. Martonosi, "Thread criticality predictors for dynamic performance, power, and resource management in chip multiprocessors," in ISCA, 2009.

- 12. R. Bitirgen et al., "Coordinated management of multiple interacting resources in CMPs: A machine learning approach," in MICRO, 2008.

- 13. B. H. Bloom, "Space/time trade-offs in hash coding with allowable errors," Communications of the ACM, vol. 13, no. 7, 1970.

- 14. R. Bryant, "Data-intensive supercomputing: The case for DISC," CMU CS Tech. Report 07-128, 2007.

- 15. Q. Cai et al., "Meeting points: Using thread criticality to adapt multicore hardware to parallel regions," in PACT, 2008.

- 16. Y. Cai et al., "FPGA-based solid-state drive prototyping platform," in FCCM, 2011.

- 17. Y. Cai et al., "Error patterns in MLC NAND flash memory: Measurement, characterization, and analysis," in DATE, 2012.

- 18. Y. Cai et al., "Flash Correct-and-Refresh: Retention-aware error management for increased flash memory lifetime," in ICCD, 2012.

- 19. Y. Cai et al., "Error analysis and retention-aware error management for NAND flash memory," Intel Technology Journal, vol. 17, no. 1, May 2013.